# **Smart Dual Current Sense Switch**

### Product Summary

|   | 3,3V μC compatible input<br>Electrostatic discharge (ESD) protection |        |                | P-DSO-12-4       |           |   |

|---|----------------------------------------------------------------------|--------|----------------|------------------|-----------|---|

|   | Low quiescent current mode                                           | I      |                |                  |           |   |

|   | Current limitation                                                   |        |                | 0.11             |           |   |

| ٠ | Open load detection                                                  | On rea | sistance       | R <sub>ON</sub>  | 0.18      | Ω |

| ٠ | Overvoltage protection                                               | Drain  | source voltage | $V_{\rm DS(AZ)}$ | 48 - 60   | V |

|   | DMOS Overtemperature protection                                      | Suppl  | y voltage      | Vs               | 4.5 – 5.5 | V |

| • | Short circuit protection                                             |        |                |                  |           |   |

### **Specific Features**

- Proportional load current sense

- IC Overtemperature warning

- 8-Bit SPI (for diagnosis and control)

- Short to GND detection

- Programmable overload behaviour

#### **General Description**

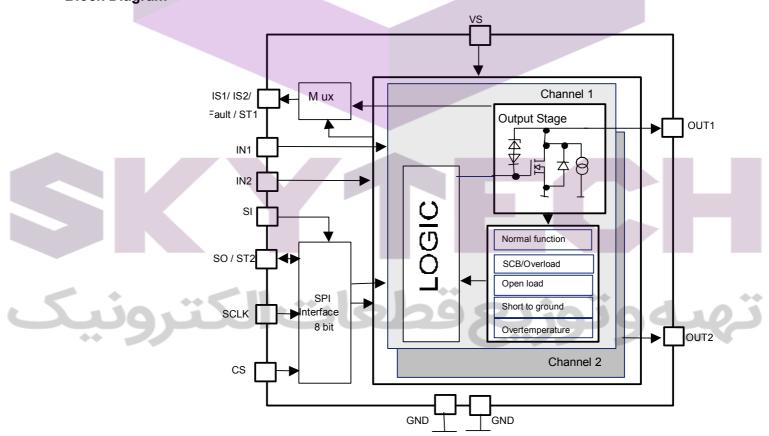

Dual Current Sense Low-Side Switch in Smart Power Technology (SPT) with two open drain DMOS output stages. The TLE 6214 L is protected by embedded protection functions and designed for automotive applications. The output stages can be controlled directly by parallel inputs for PWM applications (e.g. Oxygen Probe Heater, Stepper Motor) or by SPI. All output stages can provide a load current proportional sense signal. Diagnosis is done by an 8 bit SPI or by one status output per channel.

### **Block Diagram**

### **Pin Description**

| Pin | Symbol | Function                                  |

|-----|--------|-------------------------------------------|

| 1   | IN2    | Input Channel 2                           |

| 2   | SI     | SPI Signal In                             |

| 3   | OUT2   | Power Output Channel 2                    |

| 4   | CO1    | Current Sense 1/2 / Fault /<br>Status Ch1 |

| 5   | SCLK   | SPI Clock                                 |

| 6   | GND    | Ground                                    |

| 7   | IN1    | Input Channel 1                           |

| 8   | CS     | SPI Chip Select                           |

| 9   | OUT1   | Power Output Channel 1                    |

| 10  | VS     | Supply Voltage                            |

| 11  | CO2    | SPI Signal Out / Status Ch2               |

| 12  | GND    | Ground                                    |

### Pin Configuration (Top view)

| IN 2 | 1● | 12 | GND  |

|------|----|----|------|

| SI   | 2  | 11 | CO 2 |

| OUT2 | 3  | 10 | Vs   |

| CO 1 | 4  | 9  | OUT1 |

| SCLK | 5  | 8  | CS   |

| GND  | 6  | 7  | IN 1 |

|      |    |    |      |

Power P-DSO -12

Both GND pins and heat sink must be connected to GND externally.

# Maximum Ratings for $T_j = -40^{\circ}$ C to 150°C

| Parameter                                                                       | Symbol            | Values                      | Unit |

|---------------------------------------------------------------------------------|-------------------|-----------------------------|------|

| Supply Voltage                                                                  | Vs                | -0.3 +7                     | V    |

| Continuous Drain Source Voltage (OUT1OUT2)                                      | V <sub>DS</sub>   | -0.3 +48                    | V    |

| Input Voltage, All Inputs and Data outputs, Sense Lines                         | V <sub>IN</sub>   | - 0.3 + 7                   | V    |

| Output Current per Channel <sup>1)</sup>                                        | I <sub>D</sub>    | I <sub>D(lim1,2) min.</sub> | А    |

| Reverse Current per channel                                                     | I <sub>rev</sub>  | -3                          | А    |

| Output Clamping Energy<br>/ <sub>D</sub> = 1A                                   | E <sub>AS</sub>   | see character-<br>istic     | mJ   |

| Electrostatic Discharge Voltage (human body model)                              | V <sub>ESD</sub>  |                             |      |

| according to MIL STD 883D, method 3015.7 and EOS/ESD assn. standard S5.1 – 1993 |                   |                             |      |

| Output Pins                                                                     |                   | 4000                        | V    |

| All other Pins                                                                  |                   | 2000                        | V    |

| DIN Humidity Category, DIN 40 040                                               |                   | E                           |      |

| IEC Climatic Category, DIN IEC 68-1                                             |                   | 40/150/56                   |      |

| Thermal resistance                                                              |                   |                             |      |

| junction - case                                                                 | R <sub>thJC</sub> | 2                           | K/W  |

| junction - ambient @ min. footprint                                             | R <sub>thJA</sub> | 105                         | K/W  |

| junction - ambient @ 6 cm <sup>2</sup> cooling area                             |                   | 45                          | K/W  |

| قطعات الكتيونيك                                                                 | زيع               | ەوتو                        | بيا  |

6 cm<sup>2</sup> copper cooling area

min footprint

<sup>&</sup>lt;sup>1)</sup> Output current rating as long as maximum junction temperature is not exceeded. The maximum output current has to be calculated using  $R_{thJA}$  according mounting conditions.

# **Electrical Characteristics**

|                                                                 |                          |                               | Symbol                     | Values               |      |      | Unit |  |

|-----------------------------------------------------------------|--------------------------|-------------------------------|----------------------------|----------------------|------|------|------|--|

| $V_{\rm S} = 4.5 \rm V - 5.5 \rm V$ ; $T_{\rm j} = -40^{\circ}$ | °C to + 150              | С                             |                            | min                  | typ  | max  |      |  |

| (unless otherwise specified)                                    | led)                     |                               |                            |                      |      |      |      |  |

| 1. Power Supply                                                 |                          |                               |                            |                      |      |      |      |  |

| Supply Voltage                                                  | Supply Voltage           |                               |                            |                      |      | 5.5  |      |  |

| Supply Current                                                  | Current                  |                               |                            |                      |      | 5    | r    |  |

| Supply Current in Sleep Mod                                     | de (CS = H)              |                               | I <sub>S(sleep)</sub>      |                      |      | 10   |      |  |

| Wake up Time (after sleep n                                     | node)                    |                               | t <sub>wake</sub>          |                      |      | 100  |      |  |

| 2. Power Outputs                                                |                          |                               |                            |                      |      |      |      |  |

| ON Resistance $V_{\rm S}$ = 5 V; $I_{\rm D}$ =                  | = 2 A                    | <i>T</i> <sub>J</sub> = 25°C  | R <sub>DS(ON)</sub>        |                      | 0.18 | 0.22 |      |  |

|                                                                 |                          | <i>T</i> <sub>J</sub> = 125°C |                            |                      | 0.27 | 0.32 |      |  |

|                                                                 |                          | <i>T</i> <sub>J</sub> = 150°C |                            |                      | 0.3  | 0.36 |      |  |

| Output Clamping Voltage                                         |                          | output OFF                    | V <sub>DS(AZ)</sub>        | 48                   | -    | 60   |      |  |

| Current Limit 1: Current limit                                  | ation                    |                               | I <sub>D(lim1)</sub>       | 5                    | 6.5  | 8    |      |  |

| Current Limit 2 :Overload sw                                    | itch off                 |                               | I <sub>D(lim2)</sub>       | 9                    | 10,5 | 12   |      |  |

| Reverse Current per channe                                      | el <sup>1</sup>          |                               | Irev                       |                      |      | 2    |      |  |

| Output Leakage Current                                          | S                        | Sleep mode active             | I <sub>D(lkg)</sub>        |                      |      | 5    |      |  |

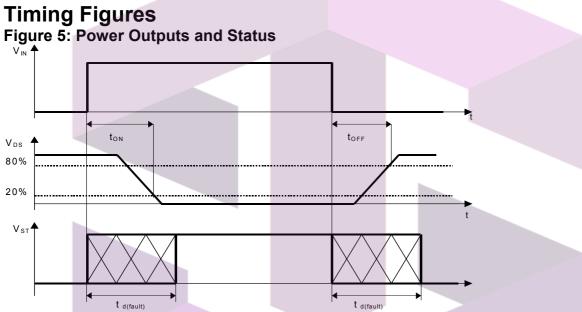

| Turn-On Time 1                                                  | I <sub>D</sub> = 2 A     | , resistive load              | t <sub>ON</sub>            |                      | 5    | 10   |      |  |

| Turn-On Time 2                                                  | $I_{\rm D} = 2  A$       | , resistive load              |                            | -                    | 20   | 50   |      |  |

| Turn-Off Time 1                                                 | $I_{\rm D} = 2  A$       | , resistive load              | t <sub>OFF</sub>           |                      | 5    | 10   |      |  |

| Turn-Off Time 2                                                 | $I_{\rm D} = 2  A$       | , resistive load              |                            |                      | 20   | 50   |      |  |

| Turn On slew rate                                               | J <sub>DS</sub> 80% to 3 | 30%, V <sub>bat</sub> = 14V   | S <sub>ON</sub>            |                      |      |      | V    |  |

| Slew rate 1                                                     | $I_{\rm D} = 2 A$        | A, resistive load             |                            | 1                    | 5    | 20   |      |  |

| Slew rate 2                                                     | $I_{\rm D} = 2  A$       | A, resistive load             |                            |                      | 1    | 5    |      |  |

| Turn Off slew rate                                              | J <sub>DS</sub> 30% to 8 | 30%, V <sub>bat</sub> = 14V   | SOFF                       |                      |      |      | V    |  |

| Slew rate 1                                                     | $I_{\rm D} = 2  A$       | A, resistive load             |                            | 1                    | 5    | 20   |      |  |

| Slew rate 2                                                     | $I_{\rm D} = 2 A$        | A, resistive load             |                            |                      | 1    | 5    |      |  |

| 3. Digital Inputs                                               |                          |                               |                            |                      | _    |      |      |  |

| Input Low Voltage                                               |                          |                               | V <sub>INL</sub>           |                      |      | 1.0  |      |  |

| Input High Voltage                                              |                          |                               | V <sub>INH</sub>           | 2.0                  |      | -    |      |  |

| Input Voltage Hysteresis                                        |                          |                               | V <sub>INHys</sub>         | 100                  | 200  | 400  |      |  |

| Input Pull Down Current (IN1                                    | 1 IN2)                   |                               | <i>I</i> <sub>IN(12)</sub> | 20                   | 50   | 100  |      |  |

| Input Pull Down Current (SI,                                    | SCLK)                    | 1 1 3                         | I <sub>IN(SI,SCLK)</sub>   | 10                   | 20   | 50   |      |  |

| Input Pull Up Current (CS)                                      |                          |                               | I <sub>IN(CS)</sub>        | 10                   | 20   | 50   |      |  |

| 4. Digital Outputs (SO, FAI                                     | JLT , Status             | 1/2)                          |                            | .//                  |      |      | 44   |  |

| SO High State Output Voltag                                     |                          | ,<br>I <sub>SOH</sub> = 2 mA  | V <sub>SOH</sub>           | V <sub>s</sub> - 0.4 |      |      | 1    |  |

| SO Low State Output Voltag                                      |                          | I <sub>SOL</sub> = 2.5 mA     | V <sub>SOL</sub>           |                      |      | 0.4  |      |  |

<sup>&</sup>lt;sup>1</sup> without loss of function, supply current can be  $I_{\rm S}$  > 5mA

| Output Tri-state Leakage Current              | $CS = H,  0 \leq V_{SO} \leq V_S$ | I <sub>SOlkg</sub> | -10 | 0 | 10  | μA  |

|-----------------------------------------------|-----------------------------------|--------------------|-----|---|-----|-----|

| FAULT Output Low Voltage                      | I <sub>FAULT</sub> = 1.6 mA       | $V_{FAULTL}$       |     |   | 0.4 | V   |

| Status Output Low Voltage                     | I <sub>ST</sub> = 1.6 mA          | V <sub>ST</sub>    |     |   | 0.4 | V   |

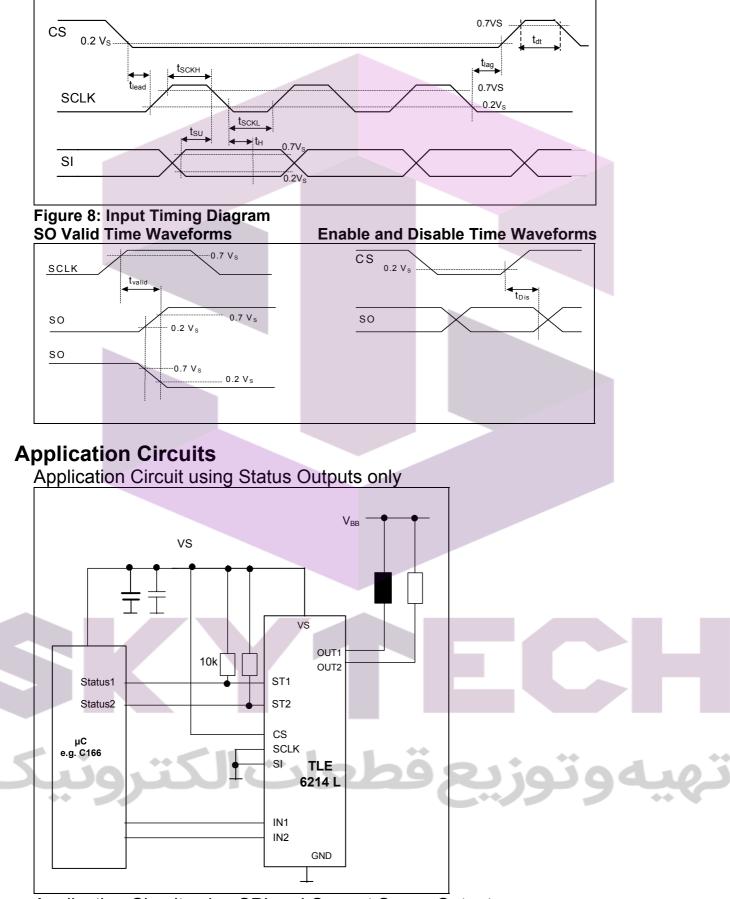

| 5. SPI                                        |                                   |                    |     |   |     |     |

| Serial Clock Frequency (depending on SO load) |                                   |                    | DC  |   | 5   | MHz |

| Serial Clock Frequency (depending on SO load)                |                         |                           | DC   | <br>5   | MHZ |

|--------------------------------------------------------------|-------------------------|---------------------------|------|---------|-----|

| Serial Clock Period (1/fsclk)                                |                         |                           | 200  | <br>    | ns  |

| Serial Clock High Time                                       |                         | <b>t</b> <sub>scкн</sub>  | 80   | <br>    | ns  |

| Serial Clock Low Time                                        |                         | <i>t</i> <sub>SCKL</sub>  | 80   | <br>-   | ns  |

| Enable Lead Time (falling edge of CS to rising edge of SCLK) |                         |                           | 200  | <br>    | ns  |

| Enable Lag Time (falling edge of SCLK to CS)                 | t <sub>lag</sub>        | 200                       | <br> | ns      |     |

| Data Setup Time (required time SI to fallin                  | <b>t</b> <sub>s∪</sub>  | 20                        | <br> | ns      |     |

| Data Hold Time (falling edge of SCLK to S                    | SI)                     | t <sub>H</sub>            | 20   | <br>    | ns  |

| Disable Time                                                 |                         | t <sub>DIS</sub>          |      | <br>150 | ns  |

| Transfer Delay Time <sup>1</sup>                             |                         | <i>t</i> <sub>dt</sub>    | 300  | <br>    | ns  |

| (CS high time between two accesses)                          |                         |                           |      |         |     |

| Data Valid Time                                              | C <sub>L</sub> = 50 pF  | <i>t</i> <sub>valid</sub> |      | <br>120 | ns  |

|                                                              | C <sub>L</sub> = 100 pF |                           |      | <br>150 |     |

|                                                              |                         |                           |      |         |     |

| 6. Diagno | stic F | unctio | ns |

|-----------|--------|--------|----|

| o. Diagno |        | anouo  |    |

| o. Diagnostici i unctions                                                                |                                   |     |            |      |     |

|------------------------------------------------------------------------------------------|-----------------------------------|-----|------------|------|-----|

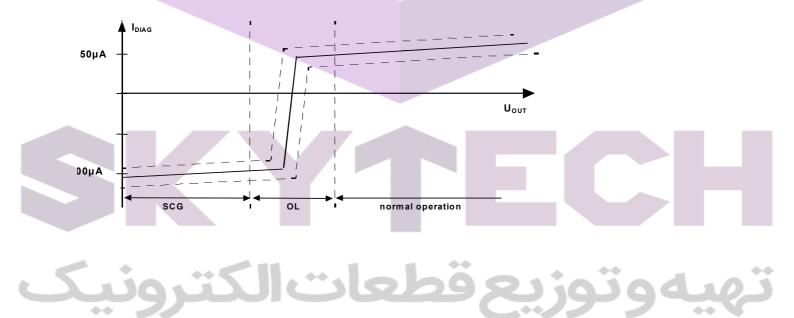

| Open Load Detection Voltage(Channel OFF)                                                 | V <sub>DS(OL)</sub>               |     | 0.6*<br>Vs |      | V   |

| Output Pull Down Current                                                                 | I <sub>PD(OL)</sub>               | 25  | 50         | 100  | μA  |

| Fault Filtering Time                                                                     | t <sub>d(fault)</sub>             | 50  | 100        | 200  | μs  |

| Overload switch off delay time (only current limit 2)                                    | T <sub>d(off)</sub>               | 10  |            | 50   | μs  |

| Short to Ground Detection Voltage                                                        | V <sub>DS(SHG)</sub>              |     | 0.4*<br>Vs |      | V   |

| Short to Ground Detection Current(Channel OFF)                                           | I <sub>SHG</sub>                  | -50 | -100       | -150 | μA  |

| Under Current Detection Threshold (Channel ON)                                           | I <sub>D(OL)</sub>                | 100 | 170        | 300  | mA  |

| Current Limit1; Overload Threshold Current1                                              | I <sub>D(lim1)</sub>              | 5   | 6.5        | 8    | A   |

| Current Limit2; Overload Threshold Current2                                              | I <sub>D(lim2)</sub>              | 9   | 10,5       | 12   | A   |

| IC Overtemperature Warning                                                               | T <sub>w</sub>                    | 155 |            | 185  | °C  |

| Hysteresis                                                                               | T(w) hys                          |     | 10         |      | K   |

| Channel Overtemperature Shutdown                                                         | $T_{ m th(sd)}$                   | 170 |            | 200  | °C  |

| Hysteresis                                                                               | T <sub>(sd</sub> ) <sub>hys</sub> |     | 10         |      | K   |

| 5. Analog Current Sense Output (IS1 / IS2)                                               |                                   | +   | ++         |      |     |

| Current Sense Precision (single channel) <sup>2</sup> I <sub>FB</sub> / I <sub>OUT</sub> | PIS                               | 0.8 | 1.0        | 1.2  | mA  |

| I <sub>D</sub> = 200mA – 1A; U <sub>CO1</sub> ≥ 2V                                       |                                   |     |            |      | / A |

<sup>&</sup>lt;sup>1</sup> This time is necessary between two write accesses. To get the correct diagnostic information, the transfer delay time has to be extended to the maximum fault delay time  $t_{d(fault)max} = 200 \mu s$ . <sup>2</sup> If the summed current is sensed the tolerances of the single channels are added.

| Current Sense Precision (single channel) <sup>3</sup> | I <sub>FB</sub> / I <sub>OUT</sub> | P <sub>IS</sub> |     |     |     | mA  |

|-------------------------------------------------------|------------------------------------|-----------------|-----|-----|-----|-----|

| I <sub>D</sub> = 1A − 5A; U <sub>CO1</sub> ≥ 2V       |                                    |                 | 0.9 | 1.0 | 1.1 | / A |

# **Functional Description**

The TLE 6214 L is a dual-low-side power switch which has two parallel inputs to control the 2 power DMOS switches, as well as by an 8-Bit SPI for control and diagnostic feedback. The power transistors are protected<sup>1)</sup> against short circuit, overload (current limitation), overtemperature and against overvoltage by an active zener clamp. The IC has a load current proportional current output for current control applications.

The diagnostic logic recognises a fault condition which can be read out via the SPI or the parallel status outputs (depending on the IC configuration).

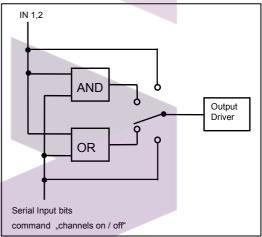

# Output Stage Control: Parallel Control or SPI Control

The Output stages can be controlled by parallel Inputs or by SPI command. The IC can be pro-

grammed (by SPI) to switch the outputs according to the parallel input signal, to the corresponding SPI command bit or to a combination of these two signals.

Both, parallel inputs and respective SPI databits are high active.

Truth table for Output control

| Input control sig- |     |  | Output Channel n |         |       |       |   |  |  |  |

|--------------------|-----|--|------------------|---------|-------|-------|---|--|--|--|

| nal Channel n      |     |  |                  |         |       |       |   |  |  |  |

| parallel           | SPI |  | parallel         | serial  | logic | logic |   |  |  |  |

| Input              | Bit |  | control          | control | OR    | AND   |   |  |  |  |

| 0                  | 0   |  | off              | off     | off   | off   |   |  |  |  |

| 0                  | 1   |  | off              | on      | on    | off   |   |  |  |  |

| 1                  | 0   |  | on               | off     | on    | off   | ] |  |  |  |

| 1                  | 1   |  | on               | on      | on    | on    |   |  |  |  |

Each output is independently controlled by an output latch. A logic high input 'data bit' turns the respective output channel ON, a logic low 'data bit' turns it OFF.

### Switching speed / Slew rate:

The switching speed / slew rate of both channels can be configured by SPI for slow or fast switching speed (1:5) for each channel individually.

### **Overtemperature Behaviour:**

Each channel has an overtemperature sensor and is individually protected against overtemperature. As soon as overtemperature occurs the channel is immediately turned off (without fault filtering time) and the overtmperature information is reported by diagnosis. In this case there are two different behaviours of the affected channel that can be selected by SPI (for all channels generally).

**Autorestart**: as long as the input signal of the channel remains on (e.g. parallel input high) the channel turns automatically on again after cooling down.

**Latching**: After overtemperature shutdown the channel stays off until the overtemperature latch is reset by a new  $L \rightarrow H$  transition of the input signal.

Note: The overtemperature sensors of the output channels are only active if the channel is turned on.

As soon as the IC temperature (Temperature of the whole IC) reaches a specified level an overtemperature warning will be indicated.

<sup>&</sup>lt;sup>1</sup>)The integrated protection functions prevent an IC destruction under fault conditions and may not be used in normal operation or permanently.

**Low Quiescent current mode (Sleep mode) :** By SPI Command the device can be set to Sleep mode. In this mode all outputs are turned off, the diagnosis and biasing is disabled, the diagnosis and the on/off register are reseted and the current consumption drastically reduced. A wake up is done by sending a wake up command by SPI. A specified time ( $t_{wake}$ ) after this command the IC is fully functional. The configuraton register (exception channel on/off register) values are not influenced by the sleep mode. After wake up the outputs are Off, except the outputs are controlled by parallel inputs. **Overload Protection:** The IC can be programmed to react in different ways to overload.

Current limit 1: In this mode the IC active limits the current to the specified "Current Limit 1". If the current limitation is active for longer than the fault filtering time this fault is reported and stored in the Fault register.

Current limit 2: If this current limit is active for more than the specified "Overload switch off delay time" the affected channel is turned off and the fault is reported and stored in the fault register. To turn on the channel again this overload latch has to be reset before with an  $L \rightarrow H$  transition of the input signal (parallel /SPI depending on the programmed operation).

The two operation modes can be changed during operation of the channel.

# **Pin description:**

**OUTPUT 1,2** – Drain pins of the two channels. Output pins and connected to the load.

**GND** – Ground pins.

IN 1,2 - Parallel Input Pins of the two channels

**IS / Fault / ST1** –Configurable output pin. Depending on the configuration (done by SPI command) it has three basic functions:

- a) General Fault pin. This is a general fault pin (open drain) which shows a high to low transition as soon as an error is latched into the diagnosis register. When the diagnosis register is cleared this flag is also reset (high state). This fault indication can be used to generate a  $\mu$ C interrupt.

- b) Sense Function. In this configuration the analog output signal represents the value of the load current: Sense Current proportional load current channel 1

- Sense Current proportional load current channel 2

- Sense Current proportional load current of both channels  $(I_{D1} + I_{D2})$

- c) Status Output for channel 1: The Status output shows the same level as the input signal of channel 1 as long as there is no error and the inverted input signal when any kind of error occurred at channel 1

**VS** – Logic Supply pin. Used to supply the integrated circuitry.

CS – Chip Select of the SPI (low active)

**SO** / **ST2** – Configurable output pin. Depending on the configuration (done by SPI command) it has two functions:

- a) Signal Output of the Serial Peripheral Interface

- b) Status Output for channel 2: The Status output shows the same level as the input signal of channel 2 as long as there is no error and the inverted input signal when any kind of error occurred at channel 2

- SI Signal Input of the Serial Peripheral Interface. The pin has an internal pull down structure.

- SCKL Clock Input of the Serial Peripheral Interface. The pin has an internal pull down structure

••

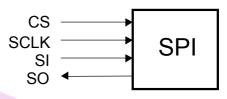

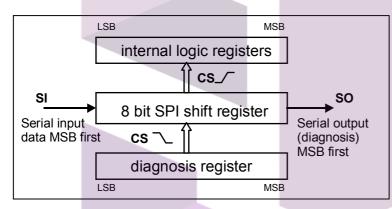

# SPI

The SPI is a **S**erial **P**eripheral Interface with 4 digital pins and an 8 bit shift register. The SPI is used to configure and program the device, turn on and off channels and to read detailed diagnostic information.

Note: The default setting of the TLE614L is to use the the SO/ST2 pin as status output pin for channel 2. To activate

the SO function of the SPI the command "I/O Configure" (see. SPI commands: No.3) has to be used to reconfigure the IC. (e.g. 0111 xxxx)

# SPI Signal Description:

**CS** - Chip Select. The system microcontroller selects the TLE 6214 L by means of the CS pin. Whenever the pin is in a logic low state, data can be transferred from the  $\mu$ C and vice versa.

**CS = H :** Any signals at the SCLK and SI pins are ignored and SO is forced into a high impedance state.

# CS = H→L :

- diagnostic information is transferred from the diagnosis register into the SPI shift register. (in sleep mode no tranfer of diagnostic information)

- serial input data can be clocked into the SPI shift register from then on

- SO changes from high impedance state

to logic high or low state corresponding to the SO bits

**CS** = L : SPI is working like a shift register. With each clock signal at the SCLK pin the state of the SI is read into the SPI shift-register (falling clock edge) and one diagnosis bit is written out of SO (rising rising edge).

CS = L→H: \_/

- transfer of SI bits from SPI shift register into the internal logic registers

- reset of diagnosis register if sent command was valid

To avoid any false clocking the serial clock input pin SCLK should be logic low state during high to low transition of CS.

**SCLK** - Serial Clock. The serial clock pin clocks the internal SPI shift register of the TLE 6214 L. The serial input (SI) accepts data into the input SPI shift register on the falling edge if while the serial output (SO) shifts diagnostic information out of the SPI shift register on the rising edge of serial clock. It is essential that the SCLK pin is in a logic low state whenever chip select CS makes any transition.

**SI** - Serial Input. Serial data bits are shifted in at this pin, the most significant bit (MSB) first. SI information is read in on the falling edge . Input data is latched in the SPI shift register and then transferred to the internal registers of the logic.

The input data consist of 8 bit, made up of x control bits and y data bits. The control word is used to program the device, to operate it in a certain mode as well as providing diagnostic information (see SPI Commands).

**SO** - Serial Output. Diagnostic data bits are shifted out serially at this pin, the most significant bit (MSB) first. SO is in a high impedance state until the CS pin goes to a logic low state. New diagnostic data will appear at the SO pin following the rising edge.

# **SPI Commands:**

| No | Command          | MSB          | 6 | 5 | 4                    | 3                    | 2          | 1        | LSB      |  |

|----|------------------|--------------|---|---|----------------------|----------------------|------------|----------|----------|--|

|    | •                | Command Bits |   |   | Data Bits            |                      |            |          |          |  |

|    |                  |              |   |   |                      |                      |            |          |          |  |

| 1  | Diagnosis only   | 0            | 0 | 1 | X                    | Х                    | Х          | Х        | Х        |  |

| 2  | Output Configure | 0            | 1 | 0 | I <sub>lim</sub> Ch2 | I <sub>lim</sub> Ch1 | Restart    | Slewrate | Slewrate |  |

|    |                  |              |   |   |                      |                      | /Latch     | Ch2      | Ch1      |  |

| 3  | I/O Configure    | 0            | 1 | 1 | Status /             | Parallel /           | Serial In- | Fault /  | Sense    |  |

|    | Ŭ                |              |   |   | SPI                  | р                    | ut         |          |          |  |

| 4  | Reset Registers  | 1            | 0 | 0 | Х                    | Х                    | Х          | Х        | Х        |  |

| 5  | Sleep Mode       | 1            | 0 | 1 | Х                    | Х                    | Х          | X        | Х        |  |

| 6  | Wake Up          | 1            | 1 | 0 | Х                    | Х                    | Х          | X        | Х        |  |

| 7  | Channels on (1)  | 1            | 1 | 1 | Ch2                  | Ch1                  | Х          | X        | Х        |  |

|    | / off (0)        |              |   |   |                      |                      |            |          |          |  |

| 8  | No command       | 0            | 0 | 0 | Х                    | Х                    | Х          | Х        | Х        |  |

**Command description:** (default values are bold print)

**1. Diagnosis Only :** Reads out the diagnosis register. This command has no other influence on the device.

2. Output Configure : Configures the behaviour of the Power Outputs.

Ilim Ch1: overload behaviour of channel 1

- 0: Current limit 2 is activated (default)

- 1: Current limit 1 is activated

Ilim Ch2: overload behaviour of channel 2

- 0: Current limit 2 is activated(default)

- 1: Current limit 1 is activated

Restart / Latch: overtemperature behaviour of the IC

0: Automatic autorestart of a channel after cooling down(default)

1: Latching "off" of a channel at overtemperature

Slew rate: Switching slew rate of channel 1 and 2

- 0: fast switching (slew rate 1) (default)

- 1: slow switching (slew rate 2)

- 3. I/O Configure : Configures the behaviour of the I/O Ports.

Status / SPI : Output of diagnostic information of the IC

- 0: Diagnosis output serial with one status output per channel (ST1, ST2)

- 1: Diagnosis output with SPI (SO) and Fault Pin / Sense Pin

Parallel / Serial Input : Control of the output channels

bit3 bit2

0

- 0 0 : Control of channel 1 and 2 with parallel input (IN1, IN2) (default)

- 1 : Control of channel 1 and 2 with combination (OR) of serial and parallel input signal

- 1 0 : Control of channel 1 and 2 with combination (AND) of serial and parallel input signal

- 1 1 : Control of channel 1 and 2 only with SPI

- Sense / Fault : Function of the Sense / Fault / ST1 output

#### bit1 bit0

- 0 0 : Pin function is "general Fault pin"(default)

- 0 1 : Pin function is current sense output channel 1 ( $I_{IS1}$ )

- 1 0 : Pin function is current sense output channel 2 ( $I_{IS2}$ )

- 1 1 : Pin function is current sense output channel 1 + 2 ( $I_{IS1}$  +  $I_{IS2}$ )

**4. Reset Registers** : Sets back all internal registers. Logic registers to default and Fault registers to no error.

Default settings after Reset:

Parallel Input control Autorestart Status Outputs ST1 and ST2 active Current Limit 2 Channel ON/OFF register "OFF" Slew rate fast

**5.** Sleep mode : Activates the low quiescent mode. In sleep mode only the command "wake up" is valid. Other commands will not lead to any reactions. Wake up is done by the Wake Up command or by undervoltage reset.

**6. Wake Up :** Deactivates the low quiescent mode. A specified time  $(t_{wake})$  after this command the IC is fully functional.

7. Channels on / off : Turns on / off the power outputs (if configured for serial control)

Ch1 : Serial control bit of channel 1 0: Output off(default) 1: Output on Ch2 : Serial control bit of channel 2 0: Output off(default) 1: Output on

After activation of the low quiescent mode by the "sleep" command, the outputs are turned off and the serial control register is set to default values.

**8. No Command** : No valid command and will not lead to an reaction (register value change, switching channels, ...) of the IC. After Chip Select giong  $L \rightarrow H$  the diagnosis register will not be reset.

# **SPI Diagnostics:**

As soon as a fault occurs for longer than the fault filtering time (exept Overtemperature; no filtering time), the fault information is latched into the diagnosis register (and the Fault pin will change from high to low state). A new error on the same channel will over-write the old error report. Serial data out pin (SO) is in a high impedance state when CS is high. If CS receives a LOW signal, all diagnosis bits can be shifted out serially. If the sent command was valid the rising edge of CS will reset all diagnosis registers and restart the fault filtering time. In case of an invalid command the device will ignore the data bits and the diagnosis register will not be reset at the rising CS edge.

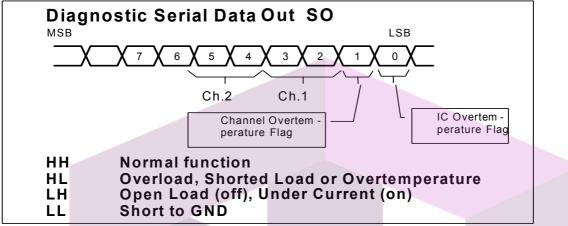

### Figure 1: Two bits per channel diagnostic feedback plus two overtemperature flags

For Full Diagnosis there are two diagnostic bits per channel configured as shown in Figure 1. Bit 6 and bit 7 of the diagnostic register are not used and always H.

**Normal function:** The bit combination **HH** indicates that there is no fault condition, i.e. normal function. **Overload, Shorted Load or Overtemperature: HL** is set when the current limitation gets active, i.e. there is a overload, short to supply or overtemperature condition. The second reason for this bit combination is overtemperature of the corresponding channel.

**Open load/ Under current: LH** is set when open load (in off state of the channel) or under current (in on state of the channel) is detected

Short to GND : LL is set when this condition is detected (in off state)

**Channel Overtemperature Flag:** In case of overtemperature in any output channel in on state the overtemperature Flag in the SPI diagnosis register is set. This Bit can be used to distinguish between Overload and Overtemperature (both HL combination).

**IC Overtemperature Warning Flag:** When the IC logic temperature exceeds typ.170° the IC Overtemperature Warning Flag will be set in the SPI diagnosis register.

# **Parallel Status Output Diagnostics :**

Parallel diagnostic outputs (open drain) change state according to the input signal of the corresponding channel. As soon as an error occurs at the corresponding channel (Overload, Overtemperature and Under current is detected in on state and Open load, short to GND also in off state) the Status output shows the inverted input signal. A fault is detected only if it lasts for longer than the fault filtering time. This fault information is not latched.

# **Diagnostic Table**

In general the status follows the input signal in normal operating conditions. If any error is detected the status is inverted.

| Operating Condition                                                         | Con-<br>trol<br>Input | Power<br>Output   | Filter<br>time         | Status<br>Output | FAULT<br>Output | SPI dia<br>feedl                         |                               |

|-----------------------------------------------------------------------------|-----------------------|-------------------|------------------------|------------------|-----------------|------------------------------------------|-------------------------------|

|                                                                             |                       |                   |                        |                  |                 | Channel<br>Diagnostic<br>bits<br>MSB LSE | Channel<br>overtemp<br>. flag |

| Sleep Mode                                                                  | X                     | off               |                        | L                | Н               |                                          | -                             |

| Normal function                                                             | L<br>H                | off<br>on         |                        | L<br>H           | H<br>H          | Н Н<br>Н Н                               | L<br>L                        |

| Short to ground <sup>1)</sup> "off"                                         | L<br>H                | off<br>on         | td(fault)<br>td(fault) | H<br>L           | L<br>L          | L L<br>L H                               | L<br>L                        |

| Open load <sup>1)</sup> "off"<br>Under current <sup>1)</sup> "on"           | L<br>H                | off<br>on         | td(fault)<br>td(fault) | H<br>L           | L<br>L          | L H<br>L H                               | L<br>L                        |

| Overload or short to supply <sup>1)</sup><br>(Current limit 1 / Limitation) | Н                     | on                | td(fault)              | L                | L               | H L                                      | L                             |

| Overload or short to supply <sup>2)</sup><br>(Current limit 2 / Shutoff)    | Н                     | off               | td(off)                | L                | L               | H L                                      | L                             |

| Overtemperature<br>(Restart mode)                                           | Н                     | off <sup>3)</sup> | no                     | L                | L               | H L                                      | Н                             |

| Overtemperature<br>(Latch mode)                                             | Н                     | off <sup>4)</sup> | no                     | L                | L               | ΗL                                       | Н                             |

Note 1) Short to ground/open load/ under current /overload/short-to-supply - events shorter than min. time td(fault) will not be latched and not reported at the diagnosis pins.

Note 2) Overload/short-to-supply - events shorter than min. time td(off) will not be latched and not reported at the diagnosis pins.

Note 3) Off as long as overtemperature occurs, restart after cooling down.

Note 4) Shutdown latch reset by falling input edge

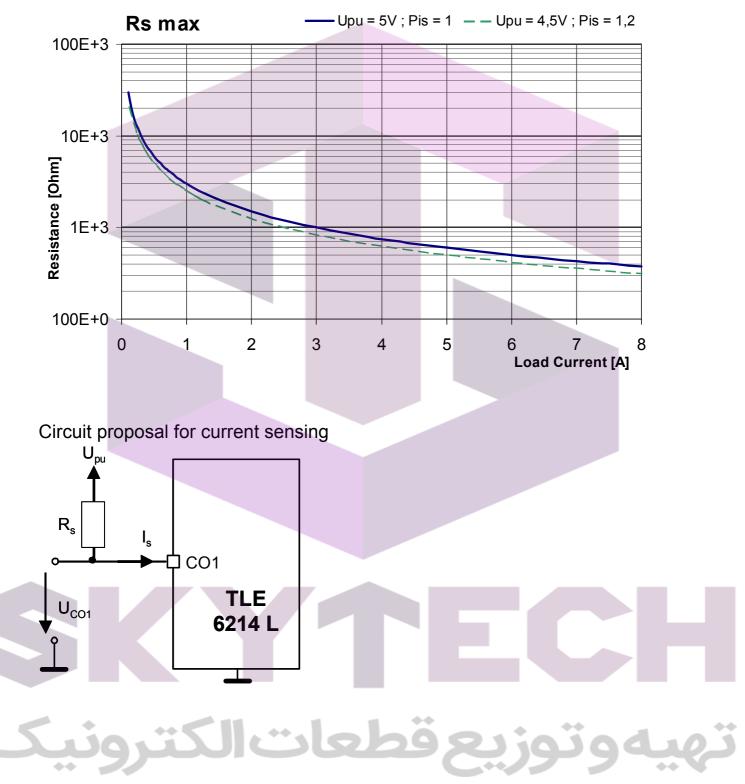

# **Analog Current Sensing :**

The TLE6214L provides an analog current sensing function for both output channels. By SPI configuration the multifunctional pin CO1 can sink a sense current proportional to the load current of one/ both of the two output channels<sup>1)</sup>. The specified current range and accuracy is described in the electrical characteristics "5. Analog Current Sense Output". To achieve the specified accuracy for current sensing the voltage at the CO1 pin must always be  $U_{CO1} \ge 2V$ .

# Figure 6: Open load (off) and Short to GND Diagnostics

<sup>&</sup>lt;sup>1)</sup> At a low load current (<<200mA) and IC configured for current sense function an offset current at the CO1 occurs (typ.  $I_S$ = 40µA @  $I_D$ =0A).

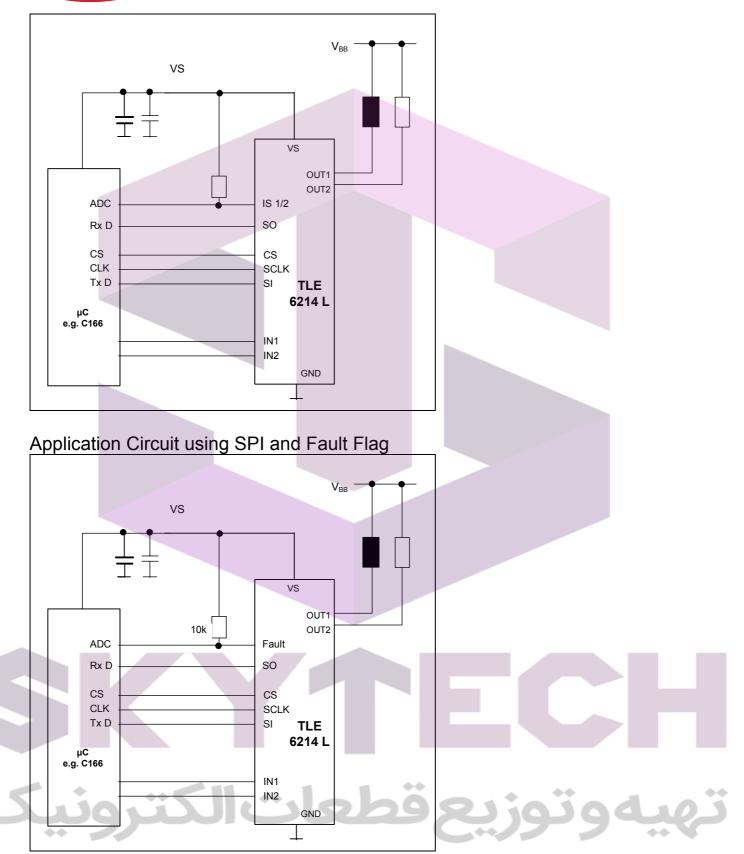

Application Circuit using SPI and Current Sense Output

# **Typical Characteristics**

Maximum Sense Resistor vs. Load Current

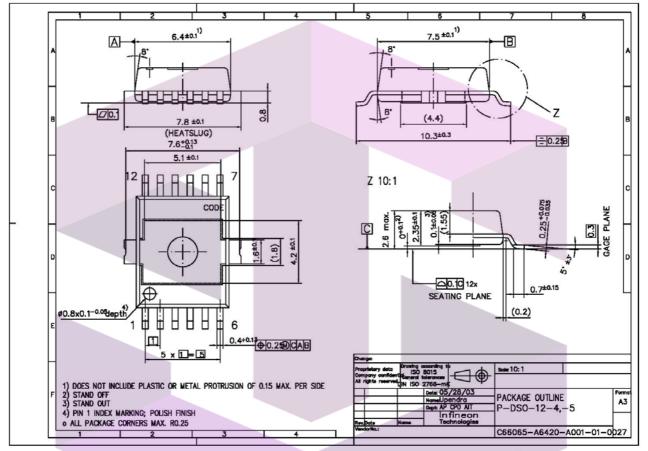

# Package and Ordering Code

- ACHANGED MARKER WITH REVISION

### (all dimensions in mm)

| P - DSO - 12 - 4 | Ordering Code |  |  |

|------------------|---------------|--|--|

| TLE 6214 L       | Q-A           |  |  |

77

V2 Preliminary

bä

#### Published by Infineon Technologies AG, Bereichs Kommunikation St.-Martin-Strasse 76.

#### D-81541 München

# © Infineon Technologies AG 1999

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.